在飛凌提供的BSP中,Nandflash采用的是FMD+PDD的結構,PDD主要是應對上層的接口,這裡我們不需要修改,直接修改FMD就好。(至於在網上看到很多人說這個結構理論上不支持MLC的Nandflash,這個暫且不說).

FMD部分的驅動源碼在 C:\WINCE600\PLATFORM\SMDK6410\src\common\nandflash\FMD\ 這個目錄下邊。

FMD的目錄結構:

nand.s

cfnand.h

fmd_LB.h(實際並沒用到)

fmd_SB.h(實際並沒用到)

nand.h

fmd.cpp

sources

makefile

先看sources文件:

[cpp]

!if 0

Copyright (c) Microsoft Corporation. All rights reserved.

!endif

!if 0

Use of this sample source code is subject to the terms of the Microsoft

license agreement under which you licensed this sample source code. If

you did not accept the terms of the license agreement, you are not

authorized to use this sample source code. For the terms of the license,

please see the license agreement between you and Microsoft or, if applicable,

see the LICENSE.RTF on your install media or the root of your tools installation.

THE SAMPLE SOURCE CODE IS PROVIDED "AS IS", WITH NO WARRANTIES.

!endif

!IF 0

Module Name:

sources.

Abstract:

This file specifies the target component being built and the list of

sources files needed to build that component. Also specifies optional

compiler switches and libraries that are unique for the component being

built.

!ENDIF

TARGETNAME=nandflash_lib11

TARGETTYPE=LIBRARY

RELEASETYPE=PLATFORM

SYNCHRONIZE_BLOCK=1

WINCEOEM=1

WINCECPU=1

NOMIPS16CODE=1

ADEFINES=-pd "_TGTCPU SETS \"$(_TGTCPU)\"" $(ADEFINES)

LDEFINES=-subsystem:native /DEBUG /DEBUGTYPE:CV /FIXED:NO

INCLUDES=$(INCLUDES)

SOURCES=\

fmd.cpp

ARM_SOURCES=\

nand.s

這個代碼是飛凌提供的,且看這一句 TARGETNAME=nandflash_lib11,經查實,FMD+PDD使用的是FMD產生的nandflash_lib.lib庫文件,而不是nandflash_lib11.lib文件,這也說明飛凌在這方面留了一手,並沒有直接提供可用的源碼,而是給了一個lib庫給我們。

在這裡,我們需要把 TARGETNAME=nandflash_lib11 修改為 TARGETNAME=nandflash_lib

cfnand.h文件:

[cpp]

/*+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

THIS CODE AND INFORMATION IS PROVIDED "AS IS" WITHOUT WARRANTY OF

ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED TO

THE IMPLIED WARRANTIES OF MERCHANTABILITY AND/OR FITNESS FOR A

PARTICULAR PURPOSE.

Copyright (c) 2001 Microsoft Corporation

Module Name: S3C6410.H

Abstract: FLASH Media Driver Interface Samsung S3C6410 CPU with NAND Flash

controller.

Environment: As noted, this media driver works on behalf of the FAL to directly

access the underlying FLASH hardware. Consquently, this module

needs to be linked with FLASHFAL.LIB to produce the device driver

named FLASHDRV.DLL.

-----------------------------------------------------------------------------*/

#ifndef _S3C6410_CFNAND_H

#define _S3C6410_CFNAND_H

#include "FMD_LB.h"

#include "FMD_SB.h"

#include "nand.h"

#define BW_X08 (0)

#define BW_X16 (1)

#define BW_X32 (2)

#define MAX_SECTORS_PER_PAGE (8)

/*****************************************************************************/

/* S3C6410 Nand Flash Internal Data Structure Definition */

/*****************************************************************************/

typedef struct

{

UINT16 nMID; /* Manufacturer ID */

UINT16 nDID; /* Device ID */

UINT16 nNumOfBlks; /* Number of Blocks */

UINT16 nPgsPerBlk; /* Number of Pages per block */

UINT16 nSctsPerPg; /* Number of Sectors per page */

UINT16 nNumOfPlanes; /* Number of Planes */

UINT16 nBlksInRsv; /* The Number of Blocks in Reservior for Bad Blocks */

UINT8 nBadPos; /* BadBlock Information Poisition*/

UINT8 nLsnPos; /* LSN Position */

UINT8 nECCPos; /* ECC Policy : HW_ECC, SW_ECC */

UINT16 nBWidth; /* Nand Organization X8 or X16 */

UINT16 nTrTime; /* Typical Read Op Time */

UINT16 nTwTime; /* Typical Write Op Time */

UINT16 nTeTime; /* Typical Erase Op Time */

UINT16 nTfTime; /* Typical Transfer Op Time */

} FlashDevSpec;

static FlashDevSpec astNandSpec[] = {

/*************************************************************************/

/* nMID, nDID, */

/* nNumOfBlks */

/* nPgsPerBlk */

/* nSctsPerPg */

/* nNumOfPlanes */

/* nBlksInRsv */

/* nBadPos */

/* nLsnPos */

/* nECCPos */

/* nBWidth */

/* nTrTime */

/* nTwTime */

/* nTeTime */

/* nTfTime*/

/*************************************************************************/

/* 8Gbit DDP NAND Flash */

//{ 0xEC, 0xD3, 8192, 64, 4, 2,160, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0xD3, 4096, 128, 4, 2,160, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

/* 16Gbit DDP NAND Flash */

{ 0xEC, 0xD5, 4096, 128, 8, 2,160, 0, 2, 8, BW_X08, 50, 350, 2000, 50}, // 8192 gjl

/* 4Gbit DDP NAND Flash */

{ 0xEC, 0xAC, 4096, 64, 4, 2, 80, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0xDC, 4096, 64, 4, 2, 80, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

//{ 0xEC, 0xBC, 4096, 64, 4, 2, 80, 0, 2, 8, BW_X16, 50, 350, 2000, 50},

//{ 0xEC, 0xCC, 4096, 64, 4, 2, 80, 0, 2, 8, BW_X16, 50, 350, 2000, 50},

/* 2Gbit NAND Flash */

{ 0xEC, 0xAA, 2048, 64, 4, 1, 40, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0xDA, 2048, 64, 4, 1, 40, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

//{ 0xEC, 0xBA, 2048, 64, 4, 1, 40, 0, 2, 8, BW_X16, 50, 350, 2000, 50},

//{ 0xEC, 0xCA, 2048, 64, 4, 1, 40, 0, 2, 8, BW_X16, 50, 350, 2000, 50},

/* 2Gbit DDP NAND Flash */

{ 0xEC, 0xDA, 2048, 64, 4, 2, 40, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0xAA, 2048, 64, 4, 2, 40, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

//{ 0xEC, 0xBA, 2048, 64, 4, 2, 40, 0, 2, 8, BW_X16, 50, 350, 2000, 50},

//{ 0xEC, 0xCA, 2048, 64, 4, 2, 40, 0, 2, 8, BW_X16, 50, 350, 2000, 50},

/*1Gbit NAND Flash */

{ 0xEC, 0xA1, 1024, 64, 4, 1, 20, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0xF1, 1024, 64, 4, 1, 20, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

//{ 0xEC, 0xB1, 1024, 64, 4, 1, 20, 0, 2, 8, BW_X16, 50, 350, 2000, 50},

//{ 0xEC, 0xC1, 1024, 64, 4, 1, 20, 0, 2, 8, BW_X16, 50, 350, 2000, 50},

/* 1Gbit NAND Flash */

{ 0xEC, 0x79, 8192, 32, 1, 4,120, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0x78, 8192, 32, 1, 4,120, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

//{ 0xEC, 0x74, 8192, 32, 1, 4,120,11, 0, 6, BW_X16, 50, 350, 2000, 50},

//{ 0xEC, 0x72, 8192, 32, 1, 4,120,11, 0, 6, BW_X16, 50, 350, 2000, 50},

/* 512Mbit NAND Flash */

{ 0xEC, 0x76, 4096, 32, 1, 4, 70, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0x36, 4096, 32, 1, 4, 70, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

/* 512Mbit XP Card */

{ 0x98, 0x76, 4096, 32, 1, 4, 70, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

{ 0x98, 0x79, 4096, 32, 1, 4, 70, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

//{ 0xEC, 0x56, 4096, 32, 1, 4, 70,11, 0, 6, BW_X16, 50, 350, 2000, 50},

//{ 0xEC, 0x46, 4096, 32, 1, 4, 70,11, 0, 6, BW_X16, 50, 350, 2000, 50},

/* 256Mbit NAND Flash */

{ 0xEC, 0x75, 2048, 32, 1, 1, 35, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0x35, 2048, 32, 1, 1, 35, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

//{ 0xEC, 0x55, 2048, 32, 1, 1, 35,11, 0, 6, BW_X16, 50, 350, 2000, 50},

//{ 0xEC, 0x45, 2048, 32, 1, 1, 35,11, 0, 6, BW_X16, 50, 350, 2000, 50},

/* 128Mbit NAND Flash */

{ 0xEC, 0x73, 1024, 32, 1, 1, 20, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

{ 0xEC, 0x33, 1024, 32, 1, 1, 20, 5, 0, 6, BW_X08, 50, 350, 2000, 50},

//{ 0xEC, 0x53, 1024, 32, 1, 1, 20,11, 0, 6, BW_X16, 50, 350, 2000, 50},

//{ 0xEC, 0x43, 1024, 32, 1, 1, 20,11, 0, 6, BW_X16, 50, 350, 2000, 50},

{ 0x00, 0x00, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0}

};

#endif _S3C6410_CFNAND_H

且看

[cpp]

/* 16Gbit DDP NAND Flash */

0xEC, 0xD5, 4096, 128, 8, 2,160, 0, 2, 8, BW_X08, 50, 350, 2000, 50}

這裡就是使用的2G(16/8 bit=2byte) Nandflash K9GAG08U0D的一些參數配置,其中 0xEC, 0xD5表示的是Nandflash的ID號,總共有4096個block,每個block有128個page,每個page有8個sector

要支持4G(K9LBG08U0D) 的話,則加上下面的配置:

[cpp] view plaincopy

/* 32Gbit DDP NAND Flash */

{ 0xEC, 0xD7, 8192, 128, 8, 1,160, 0, 2, 8, BW_X08, 50, 350, 2000, 50},

在看nand.h文件之前,我們先來看一下fmd.cpp中引用的#include "s3c6410_nand.h"頭文件:(該文件在C:\WINCE600\PLATFORM\COMMON\SRC\SOC\S3C6410_SEC_V1\OAL\INC\s3c6410_nand.h)

[cpp]

//

// Copyright (c) Microsoft Corporation. All rights reserved.

//

//

// Use of this source code is subject to the terms of the Microsoft end-user

// license agreement (EULA) under which you licensed this SOFTWARE PRODUCT.

// If you did not accept the terms of the EULA, you are not authorized to use

// this source code. For a copy of the EULA, please see the LICENSE.RTF on your

// install media.

//

//------------------------------------------------------------------------------

//

// Header: s3c6410_nand.h

//

// Defines the NAND controller CPU register layout and definitions.

//

#ifndef __S3C6410_NAND_H

#define __S3C6410_NAND_H

#if __cplusplus

extern "C"

{

#endif

//------------------------------------------------------------------------------

// Type: S3C6410_NAND_REG

//

// NAND Flash controller register layout. This register bank is located

// by the constant CPU_BASE_REG_XX_NAND in the configuration file

// cpu_base_reg_cfg.h.

//

typedef struct

{

UINT32 NFCONF; //0x00 // configuration reg

UINT32 NFCONT; //0x04

UINT8 NFCMD; //0x08 // command set reg

UINT8 d0[3];

UINT8 NFADDR; //0x0C // address set reg

UINT8 d1[3];

UINT8 NFDATA; //0x10 // data reg

UINT8 d2[3];

UINT32 NFMECCD0; //0x14

UINT32 NFMECCD1; //0x18

UINT32 NFSECCD; //0x1C

UINT32 NFSBLK; //0x20

UINT32 NFEBLK; //0x24 // error correction code 2

UINT32 NFSTAT; //0x28 // operation status reg

UINT32 NFECCERR0; //0x2C

UINT32 NFECCERR1; //0x30

UINT32 NFMECC0; //0x34 // error correction code 0

UINT32 NFMECC1; //0x38 // error correction code 1

UINT32 NFSECC; //0x3C

UINT32 NFMLCBITPT; //0x40

} S3C6410_NAND_REG, *PS3C6410_NAND_REG;

#if __cplusplus

}

#endif

#endif

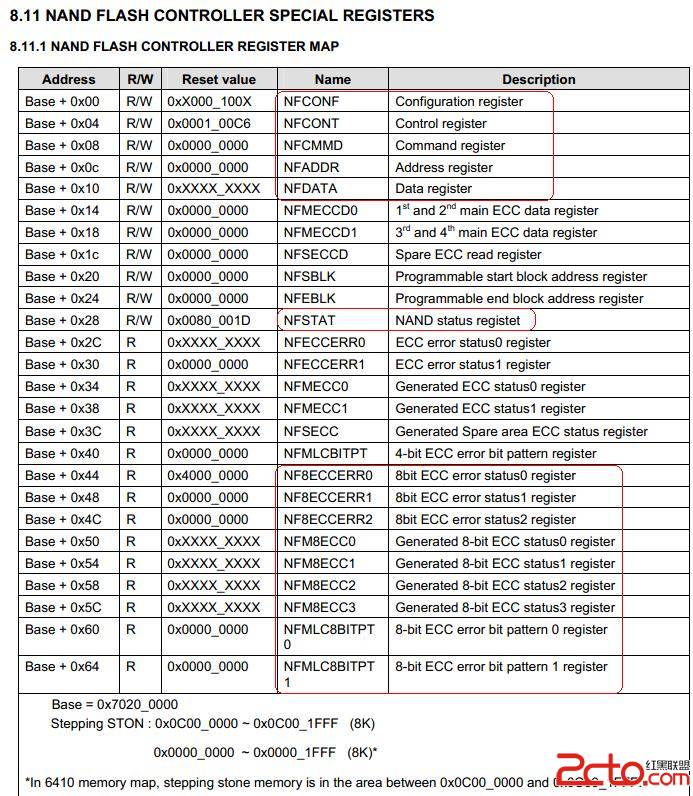

注意到了麽?這個跟文檔中的寄存器少了8bit ECC寄存器部分。

暈菜了吧,飛凌的這個2G 256M的BSP的Nandflash源碼既然是這個樣子,為什麼還在那裡號稱8bit的ECC,還說開放源碼。

靠別人都行的話,母豬都會上樹啦!咱還是自己搞吧!

在上面UINT32 NFMLCBITPT; //0x40 的後面添加以下代碼:

[cpp] //0x44-- 8位ECC錯誤狀態0寄存器

UINT32 NF8ECCERR1; //0x48-- 8位ECC錯誤狀態1寄存器

UINT32 NF8ECCERR2; //0x4c-- 8位ECC錯誤狀態2寄存器

UINT32 NFM8ECC0; //0x50-- 生成8位ECC狀態0寄存器

UINT32 NFM8ECC1; //0x54-- 生成8位ECC狀態1寄存器

UINT32 NFM8ECC2; //0x58-- 生成8位ECC狀態2寄存器

UINT32 NFM8ECC3; //0x5c-- 生成8位ECC狀態3寄存器

UINT32 NFMLC8BITPT0; //0x60-- 8位ECC錯誤位模式寄存器0

UINT32 NFMLC8BITPT1; //0x64-- 8位ECC錯誤位模式寄存器1

nand.h文件:

[cpp]

//

// Copyright (c) Microsoft Corporation. All rights reserved.

//

//

// Use of this sample source code is subject to the terms of the Microsoft

// license agreement under which you licensed this sample source code. If

// you did not accept the terms of the license agreement, you are not

// authorized to use this sample source code. For the terms of the license,

// please see the license agreement between you and Microsoft or, if applicable,

// see the LICENSE.RTF on your install media or the root of your tools installation.

// THE SAMPLE SOURCE CODE IS PROVIDED "AS IS", WITH NO WARRANTIES.

//

#ifndef __NAND_H__

#define __NAND_H__

//-----------------------------------------------------------------------------

typedef struct

{

UINT16 nNumOfBlks;

UINT16 nPagesPerBlk;

UINT16 nSctsPerPage;

} NANDDeviceInfo;

NANDDeviceInfo stDeviceInfo;

#ifdef __cplusplus

extern "C" {

#endif

NANDDeviceInfo GetNandInfo(void);

#ifdef __cplusplus

}

#endif

#define NUM_OF_BLOCKS (stDeviceInfo.nNumOfBlks)

#define PAGES_PER_BLOCK (stDeviceInfo.nPagesPerBlk)

#define SECTORS_PER_PAGE (stDeviceInfo.nSctsPerPage)

#undef SECTOR_SIZE

#define SECTOR_SIZE (512)

#define NAND_SECTOR_SIZE (SECTOR_SIZE*SECTORS_PER_PAGE)

#define NAND_PAGE_SIZE (SECTOR_SIZE*SECTORS_PER_PAGE) //< Physical Page Size

#define IS_LB ((SECTORS_PER_PAGE == 4)||(SECTORS_PER_PAGE == 8))

//-----------------------------------------------------------------------------

#define USE_NFCE (0)

#define USE_GPIO (0)

#define TACLS (NAND_TACLS)

#define TWRPH0 (NAND_TWRPH0)

#define TWRPH1 (NAND_TWRPH1)

#define ECCType (23)

//-----------------------------------------------------------------------------

#define CMD_READID (0x90) // ReadID

#define CMD_READ (0x00) // Read

#define CMD_READ2 (0x50) // Read2

#define CMD_READ3 (0x30) // Read3

#define CMD_RESET (0xff) // Reset

#define CMD_ERASE (0x60) // Erase phase 1

#define CMD_ERASE2 (0xd0) // Erase phase 2

#define CMD_WRITE (0x80) // Write phase 1

#define CMD_WRITE2 (0x10) // Write phase 2

#define CMD_STATUS (0x70) // STATUS

#define CMD_RDI (0x85) // Random Data Input

#define CMD_RDO (0x05) // Random Data Output

#define CMD_RDO2 (0xE0) // Random Data Output

#define BADBLOCKMARK (0x00)

// Status bit pattern

#define STATUS_READY (0x40) // Ready

#define STATUS_ERROR (0x01) // Error

#define STATUS_ILLACC (0x20) // Illigar Access

#define NF_ECCERR0_ALL_FF 0x40000000

#define NF_ECCERR0_ECC_READY 0x20000000

//-----------------------------------------------------------------------------

#define NF_CMD(cmd) {g_pNFConReg->NFCMD = (unsigned char)(cmd);}

#define NF_ADDR(addr) {g_pNFConReg->NFADDR = (unsigned char)(addr);}

#define NF_nFCE_L() {g_pNFConReg->NFCONT &= ~(1<<1);}

#define NF_nFCE_H() {g_pNFConReg->NFCONT |= (1<<1);}

#define NF_ECC_DIRECTION_IN() {g_pNFConReg->NFCONT &= ~(1<<18);}

#define NF_ECC_DIRECTION_OUT() {g_pNFConReg->NFCONT |= (1<<18);}

#define NF_ECC_8BIT_STOP() {g_pNFConReg->NFCONT |= (1<<12);} //stop the last encode or decode of 8bit mode.

#define NF_RSTECC() {g_pNFConReg->NFCONT |= ((1<<5) | (1<<4));}

#define NF_MSGLENGTH_512() {g_pNFConReg->NFCONF &= ~(1<<25);}

#define NF_MSGLENGTH_24() {g_pNFConReg->NFCONF |= (1<<25);}

#define NF_ECCTYPE_CLR (g_pNFConReg->NFCONF &= ~(3<<23))

#define NF_ECCTYPE_1BIT() {NF_ECCTYPE_CLR;}

#define NF_ECCTYPE_4BIT() {NF_ECCTYPE_CLR |= (1<<24);}

#define NF_ECCTYPE_8BIT() {NF_ECCTYPE_CLR |= (1<<23);}

#define NF_MECC_UnLock() {g_pNFConReg->NFCONT &= ~(1<<7);}

#define NF_MECC_Lock() {g_pNFConReg->NFCONT |= (1<<7);}

#define NF_SECC_UnLock() {g_pNFConReg->NFCONT &= ~(1<<6);}

#define NF_SECC_Lock() {g_pNFConReg->NFCONT |= (1<<6);}

#define NF_CLEAR_RB() {g_pNFConReg->NFSTAT |= (1<<4);} // Have write '1' to clear this bit.

#define NF_DETECT_RB() {while((g_pNFConReg->NFSTAT&0x11)!=0x11);} // RnB_Transdetect & RnB

#define NF_WAITRB() {while (!(g_pNFConReg->NFSTAT & (1<<0))) ; }

#define NF_RDDATA_BYTE() (g_pNFConReg->NFDATA)

#define NF_RDDATA_WORD() (*(UINT32 *)0xb0200010)

#define NF_WRDATA_BYTE(data) {g_pNFConReg->NFDATA = (UINT8)(data);}

#define NF_WRDATA_WORD(data) {*(UINT32 *)0xb0200010 = (UINT32)(data);}

#define NF_RDMECC0() (g_pNFConReg->NFMECC0)

#define NF_RDMECC1() (g_pNFConReg->NFMECC1)

#define NF_RDSECC() (g_pNFConReg->NFSECC)

#define NF_RDM8ECC0() (g_pNFConReg->NFM8ECC0)

#define NF_RDM8ECC1() (g_pNFConReg->NFM8ECC1)

#define NF_RDM8ECC2() (g_pNFConReg->NFM8ECC2)

#define NF_RDM8ECC3() (g_pNFConReg->NFM8ECC3)

#define NF_RDMECCD0() (g_pNFConReg->NFMECCD0)

#define NF_RDMECCD1() (g_pNFConReg->NFMECCD1)

#define NF_RDSECCD() (g_pNFConReg->NFSECCD)

#define NF_ECC_ERR0 (g_pNFConReg->NFECCERR0)

#define NF_ECC_ERR1 (g_pNFConReg->NFECCERR1)

#define NF_ECC8BIT_NUM ((g_pNFConReg->NF8ECCERR0 & (0xf<<25))>>25)

#define NF_ECC8LOCATION_BYTE1 (g_pNFConReg->NF8ECCERR0 & (0x3ff))

#define NF_ECC8LOCATION_BYTE2 ((g_pNFConReg->NF8ECCERR0 & (0x3ff<<15))>>15)

#define NF_ECC8LOCATION_BYTE3 (g_pNFConReg->NF8ECCERR1 & (0x3ff))

#define NF_ECC8LOCATION_BYTE4 ((g_pNFConReg->NF8ECCERR1 & (0x3ff<<11))>>11)

#define NF_ECC8LOCATION_BYTE5 ((g_pNFConReg->NF8ECCERR1 & (0x3ff<<22))>>22)

#define NF_ECC8LOCATION_BYTE6 (g_pNFConReg->NF8ECCERR2 & (0x3ff))

#define NF_ECC8LOCATION_BYTE7 ((g_pNFConReg->NF8ECCERR2 & (0x3ff<<11))>>11)

#define NF_ECC8LOCATION_BYTE8 ((g_pNFConReg->NF8ECCERR2 & (0x3ff<<22))>>22)

#define NF_ECC8LOCATION_BIT(n) (n <= 4)?((g_pNFConReg->NFMLC8BITPT0 & (0xff<<((n-1)*8)))>>((n-1)*8)):((g_pNFConReg->NFMLC8BITPT1 & (0xff<<((n-5)*8)))>>((n-5)*8))

#define NF_ECC4BIT_NUM ((g_pNFConReg->NFECCERR0 & (0x7<<26))>>26)

#define NF_ECC4LOCATION_BYTE(n) ((n <= 2)?((g_pNFConReg->NFECCERR0 & (0x3ff<<((n-1)*16)))>>((n-1)*16)):((g_pNFConReg->NFECCERR1 & (0x3ff<<((n-3)*16)))>>((n-3)*16)))

#define NF_ECC4LOCATION_BIT(n) ((g_pNFConReg->NFMLCBITPT & (0xff<<((n-1)*8)))>>((n-1)*8))

#define NF_WRMECCD0(data) {g_pNFConReg->NFMECCD0 = (data);}

#define NF_WRMECCD1(data) {g_pNFConReg->NFMECCD1 = (data);}

#define NF_WRSECCD(data) {g_pNFConReg->NFSECCD = (data);}

#define NF_RDSTAT (g_pNFConReg->NFSTAT)

//-----------------------------------------------------------------------------

typedef enum

{

ECC_CORRECT_MAIN = 0, // correct Main ECC

ECC_CORRECT_SPARE1 = 1, // correct Spare for Sector Info using Main ECC Result Area

ECC_CORRECT_SPARE2 = 2, // correct Spare for MECC using Main ECC Result Area

ECC_CORRECT_SPARE = 3 // correct Spare using Spare ECC Result Area

} ECC_CORRECT_TYPE;

//-----------------------------------------------------------------------------

#endif // __NAND_H_.

nand.h文件裡有8bit ECC的相關定義,不要高興的太早,這裡面是有錯滴,不知道是不是飛凌那邊故意搞錯的,還是本來就不是6410的。

且看定義:

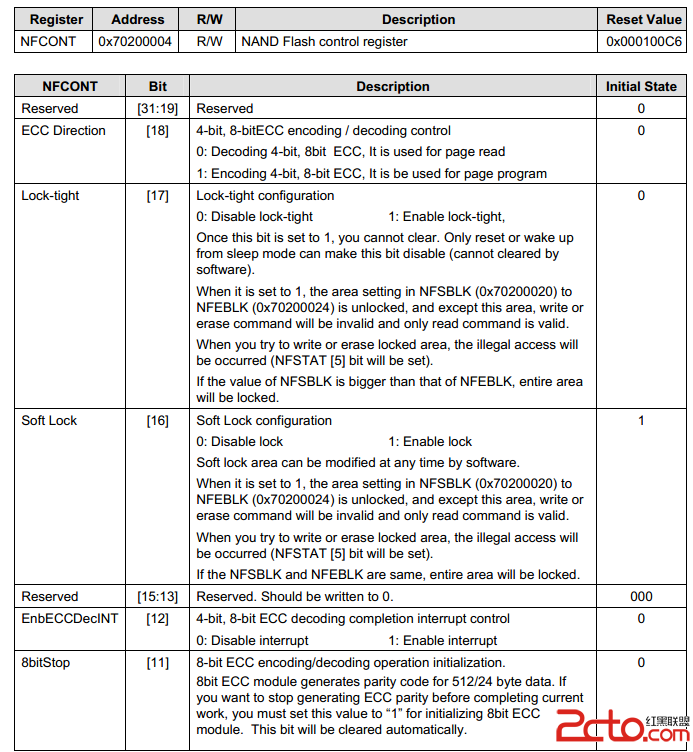

#define NF_ECC_8BIT_STOP() {g_pNFConReg->NFCONT |= (1<<12);} //stop the last encode or decode of 8bit mode.

對比文檔看一下這個NFCONT[12]是干什麼的

NFCONT[11]這個才是8bitStop,但為什麼源碼中要定義NFCONT[12]為NF_ECC_8BIT_STOP,這個容易讓人產生誤解。咱還是改一下吧!

#define NF_ECC_8BIT_STOP() {g_pNFConReg->NFCONT |= (1<<11);}