接《MSP430學習筆記1-I/O端口》

開發版型號:SEED—MSP430F5529A

開發工具 :CCS 5.4v

以下內容是CCS中ADC12操作的一些簡單的demo,現整理如下:

有關MSP430F5529芯片ADC12相關資料,可參考《MSP430x5xx and MSP430x6xx Family User's Guide (Rev. M)——Chapter 28 ADC12_A》

1:demo描述

參考AVcc電壓、以A0定時器作為采樣輸入信號源的、單通道單次模式采樣,當采樣信號大於0.5*AVcc時,P1.0置位,否則為0。 代碼如下:Description: A single sample is made on A0 with reference to AVcc.

Software sets ADC12SC to start sample and conversion - ADC12SC

automatically cleared at EOC. ADC12 internal oscillator times sample (16x)

and conversion. In Mainloop MSP430 waits in LPM0 to save power until ADC12

conversion complete, ADC12_ISR will force exit from LPM0 in Mainloop on

reti. If A0 > 0.5*AVcc, P1.0 set, else reset.

#include <msp430.h>

main( WDTCTL = WDTPW + WDTHOLD;

ADC12CTL0 = ADC12SHT02 + ADC12ON;

ADC12CTL1 = ADC12SHP;

ADC12IE = ;

ADC12CTL0 |= P6SEL |= ;

P1DIR |= ;

( ADC12CTL0 |= ADC12SC;

__bis_SR_register(LPM0_bits + GIE);

__no_operation();

vector = ADC12_VECTOR

__interrupt ADC12_ISR( (__even_in_range(ADC12IV, : ;

: ;

: ;

:

(ADC12MEM0 >= )

P1OUT |= BIT0;

P1OUT &= ~BIT0;

__bic_SR_register_on_exit(LPM0_bits);

: ;

: ;

: ;

: ;

: ;

: ;

: ;

: ;

: ;

: ;

: ;

: ;

: ;

: ;

: }

2:代碼分析

1)主函數中代碼:

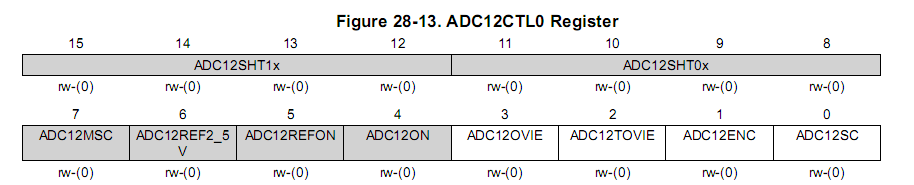

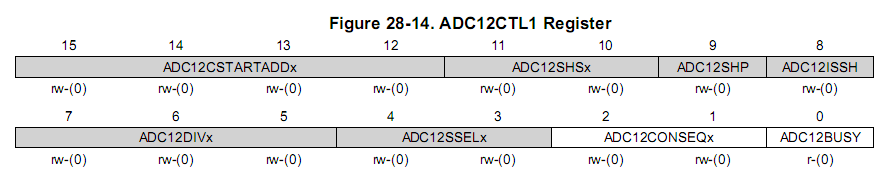

ADC12CTL0 = ADC12SHT02 + ADC12ON; ADC12CTL1 = ADC12SHP; ADC12IE = ; ADC12CTL0 |= ADC12CTL0 |= ADC12SC;參考控制寄存器如下:

ADCSHT0x :采樣保持定時器0,該四位定義了保存在轉換存儲寄存器中轉換結果的采樣周期;

ADC12ENC:轉換允許

ADC12SHP:選擇采樣定時器A0輸出

ADC12IE:中斷允許 (來自中斷允許寄存器)

ADCSHT0x :采樣保持定時器0,該四位定義了保存在轉換存儲寄存器中轉換結果的采樣周期;

ADC12ENC:轉換允許

ADC12SHP:選擇采樣定時器A0輸出

ADC12IE:中斷允許 (來自中斷允許寄存器)

2)中斷部分代碼:

中斷寄存向量ADC12IV中的數字(0-36)用來判斷中斷標志寄存器中相關位是否置位,此時表明轉換結果已經裝入轉換存儲寄存器中,具體數字的含義參見下圖:

3)

(ADC12MEM0 >= )

P1OUT |= BIT0;

P1OUT &= ~BIT0;

參考電壓使用VCC,因為ADC精度為12位(4095),所以0x7FF(2047)就是0.5Vcc的AD值

StevenMeng

2013 6.14