高速緩沖存儲器 cache

高速緩沖存儲器 cache

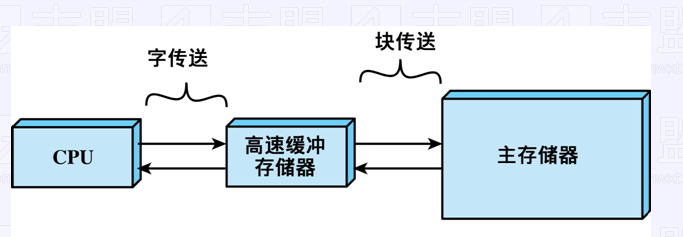

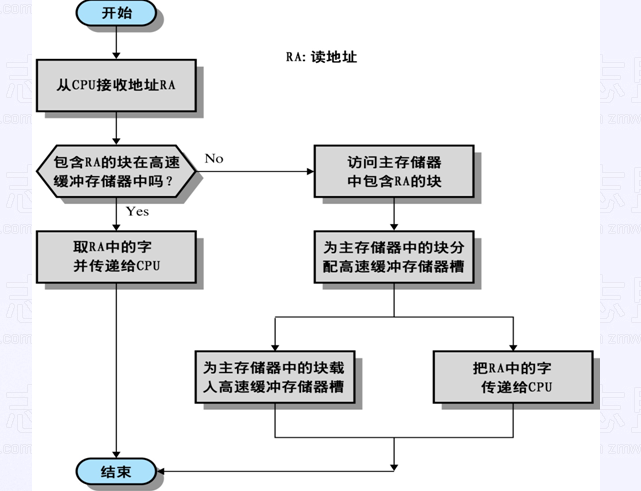

讀cache操作

讀cache操作

cache如果包含數據就直接從cache中讀出來,因為cache速度要比內存快

如果沒有包含的話,就從內存中找,找到後就放到cache中去,以後再讀的話就直接從cache讀了,下次訪問很多次的時候就會快很多,相當於提高了命中率,cpu的訪問速度就大大提高了

cache能大大提高cpu的訪問速率

cache的設計

不能太大,也不能太小

太大的話,因為程序在查看數據的時候需要把cache走一遍,如果cache太大,

那麼走一遍的時間就太長,就不能達到提升速率的效果

如果太小的話,存放在內存的塊數就少了,命中率降低,訪問內存的次數就增加了,cpu性能同樣降低了

塊大小

Cache與memory的的數據交換單位

由小變大時, 由局部性原理,命中增加

變得更大時, 新近取得數據被用到的可能性,小於那些必須被移出Cache的數據再次用到的可能性,命中率大大降低

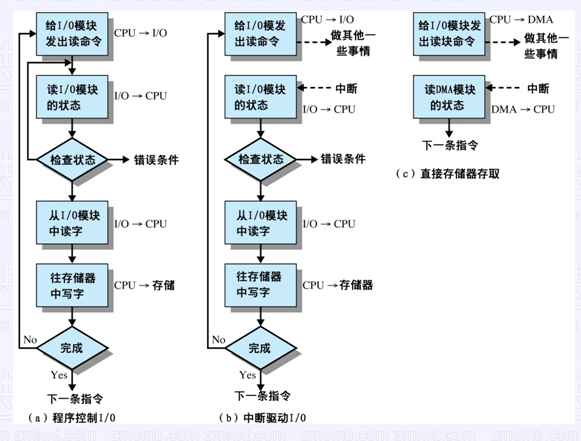

DMA

大量移動數據

cpu性能快,外設的速度比較慢,cpu就要一直等待外設

因此誕生了DMA

以前沒有DMA,就把數據從內存經過cpu到外設

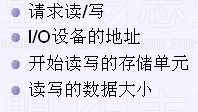

有了DMA的話,cpu把指令告訴DMA,把內存從某個地址開始,多大的數據寫給外設,這樣的話DMA就去做了,cpu就不用做了,DMA就把內存中取出數據,然後再到外設,這種機制就是DMA機制,cpu就解放了,做更重要的事,因此這種內存拷貝、數據大量移動拷貝的時候就用DMA來解放cpu,記住cpu只在開始於結束時參與

開始時:

cache如果包含數據就直接從cache中讀出來,因為cache速度要比內存快

如果沒有包含的話,就從內存中找,找到後就放到cache中去,以後再讀的話就直接從cache讀了,下次訪問很多次的時候就會快很多,相當於提高了命中率,cpu的訪問速度就大大提高了

cache能大大提高cpu的訪問速率

cache的設計

不能太大,也不能太小

太大的話,因為程序在查看數據的時候需要把cache走一遍,如果cache太大,

那麼走一遍的時間就太長,就不能達到提升速率的效果

如果太小的話,存放在內存的塊數就少了,命中率降低,訪問內存的次數就增加了,cpu性能同樣降低了

塊大小

Cache與memory的的數據交換單位

由小變大時, 由局部性原理,命中增加

變得更大時, 新近取得數據被用到的可能性,小於那些必須被移出Cache的數據再次用到的可能性,命中率大大降低

DMA

大量移動數據

cpu性能快,外設的速度比較慢,cpu就要一直等待外設

因此誕生了DMA

以前沒有DMA,就把數據從內存經過cpu到外設

有了DMA的話,cpu把指令告訴DMA,把內存從某個地址開始,多大的數據寫給外設,這樣的話DMA就去做了,cpu就不用做了,DMA就把內存中取出數據,然後再到外設,這種機制就是DMA機制,cpu就解放了,做更重要的事,因此這種內存拷貝、數據大量移動拷貝的時候就用DMA來解放cpu,記住cpu只在開始於結束時參與

開始時:

結束時:

中斷處理例程

結束時:

中斷處理例程

歡迎交流

歡迎交流

新浪博客:http://blog.sina.com.cn/u/2049150530

csdn博客:http://blog.csdn.net/u011749143

博客園:http://www.cnblogs.com/sky-heaven/

chinaUnix: http://blog.chinaunix.net/uid/30049997.html

知乎:http://www.zhihu.com/people/zhang-bing-hua